CER is a 16-bit status register, containing status information about communication errors on CAN, SPI and SCI communication channels.

TML Address: 0x0301

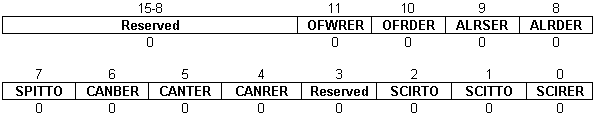

Contents. CER information is structured as follows:

Bit 15-12 Reserved

Bit 11 OFWRER.EnDat encoder offset write error

0 = |

No SPI timeout |

1 = |

SPI timeout |

Bit 10 OFRDER. EnDat encoder offset read error

0 = |

No SPI timeout |

1 = |

SPI timeout |

Bit 9 ALRSER. EnDat encoder alarm reset error

0 = |

No SPI timeout |

1 = |

SPI timeout |

Bit 8 ALRDER. EnDat encoder alarm read error

0 = |

No SPI timeout |

1 = |

SPI timeout |

Bit 7 SPITTO. SPI timeout on write operation

0 = |

No SPI timeout |

1 = |

SPI timeout |

Bit 6 CANBER. CAN bus off error

0 = |

No CAN bus off error |

1 = |

Error |

Bit 5 CANTER. CAN Tx overrun error

0 = |

No CAN transmission overrun error |

1 = |

CAN transmission overrun error |

Bit 4 CANRER. CAN Rx overrun error

0 = |

No CAN reception overrun error |

1 = |

CAN reception overrun error |

Bit 3 Reserved

Bit 2 SCIRTO. SCI Rx timeout error

0 = |

No SCI reception timeout error |

1 = |

SCI reception timeout error |

Bit 1 SCITTO. SCI Tx timeout error

0 = |

No SCI transmission timeout error |

1 = |

SCI transmission timeout error |

Bit 0 SCIRER. SCI Rx error

0 = |

No SCI reception error |

1 = |

SCI reception error |