ICR is a 16-bit command register, enabling/disabling the TML interrupts. All the unmasked bits of this register will allow the generation of a TML interrupt at the occurrence of the associated specific situation.

TML Address: 0x0304

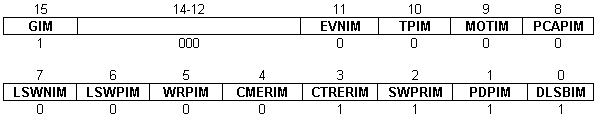

Contents. ICR information is structured as follows:

Bit 15 GIM. Globally enable/disable TML interrupts

0 = |

Disable |

1 = |

Enable |

Bit 14-12 Reserved

Bit 11 EVNIM. Enable/disable interrupt 11 – “Event set has occurred”

0 = |

Disable |

1 = |

Enable |

Bit 10 TPIM. Enable/disable interrupt 10 – “Time period has elapsed”

0 = |

Disable |

1 = |

Enable |

Bit 9 MOTIM. Enable/disable interrupt 9 – “Motion is complete”

0 = |

Disable |

1 = |

Enable |

Bit 8 PCAPIM. Enable/disable interrupt 8 – “Capture input transition detected”

0 = |

Disable |

1 = |

Enable |

Bit 7 LSWNIM. Enable/disable interrupt 7 – “LSN programmed transition detected”

0 = |

Disable |

1 = |

Enable |

Bit 6 LSWPIM. Enable/disable interrupt 6 – “LSP programmed transition detected”

0 = |

Disable |

1 = |

Enable |

Bit 5 WRPIM. Enable/disable interrupt 5 – “Position wrap around”

0 = |

Disable |

1 = |

Enable |

Bit 4 CMERIM. Enable/disable interrupt 4 – “Communication error”

0 = |

Disable |

1 = |

Enable |

Bit 3 CTRERIM. Enable/disable interrupt 3 – “Control error”

0 = |

Disable |

1 = |

Enable |

Bit 2 SWPRIM. Enable/disable interrupt 2 – “Software protection”

0 = |

Disable |

1 = |

Enable |

Bit 1 PDPIM. Enable/disable interrupt 1 –“Short-circuit”

0 = |

Disable |

1 = |

Enable |

Bit 0 DLSBIM. Enable/disable interrupt 0 – “Enable input has changed”

0 = |

Disable |

1 = |

Enable |