ISR is a 16-bit status register, containing the interrupt flags for TML interrupts. Only unmasked TML interrupts (see Interrupt Control Register - ICR) will generate a TML interrupt request.

TML Address: 0x0306

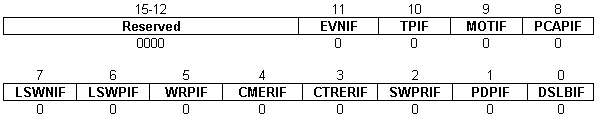

Contents. ISR information is structured as follows:

Bit 15-12 Reserved

Bit 11 EVNIF. Flag for interrupt 11 – “Event set has occurred”

0 = |

Not triggered |

1 = |

Triggered |

Bit 10 TPIF. Flag for interrupt 10 – “Time period has elapsed”

0 = |

Not triggered |

1 = |

Triggered |

Bit 9 MOTIF. Flag for interrupt 9 – “Motion is complete”

0 = |

Not triggered |

1 = |

Triggered |

Bit 8 PCAPIF. Flag for interrupt 8 – “Capture input transition detected”

0 = |

Not triggered |

1 = |

Triggered |

Bit 7 LSWNIF. Flag for interrupt 7 – “LSN programmed transition detected”

0 = |

Not triggered |

1 = |

Triggered |

Bit 6 LSWPIF. Flag for interrupt 6 – “LSP programmed transition detected”

0 = |

Not triggered |

1 = |

Triggered |

Bit 5 WRPIF. Flag for interrupt 5 – “Position wraparound”

0 = |

Not triggered |

1 = |

Triggered |

Bit 4 CMERIF. Flag for interrupt 4 – “Communication error”

0 = |

Not triggered |

1 = |

Triggered |

Bit 3 CTRERIF. Flag for interrupt 3 – “Control error”

0 = |

Not triggered |

1 = |

Triggered |

Bit 2 SWPRIF. Flag for interrupt 2 – “Software protections”

0 = |

Not triggered |

1 = |

Triggered |

Bit 1 PDPIF. Flag for interrupt 1 – “Short-circuit”

0 = |

Not triggered |

1 = |

Triggered |

Bit 0 DSLBIF. Flag for interrupt 0 – “Enable input has changed”

0 = |

Not triggered |

1 = |

Triggered |